### MAX30009

Click here to ask an associate for production status of specific part numbers.

# Low-Power, High-Performance Bioimpedance Analog Front-End

### **General Description**

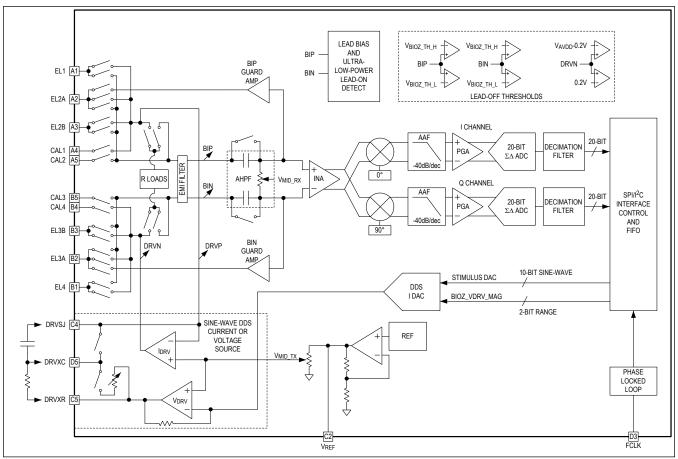

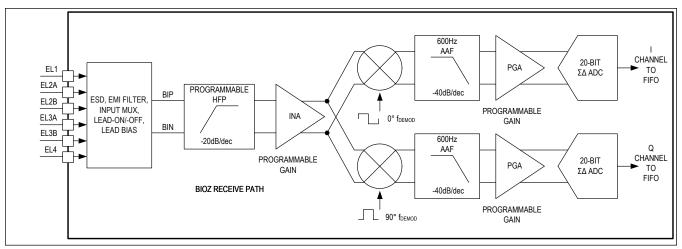

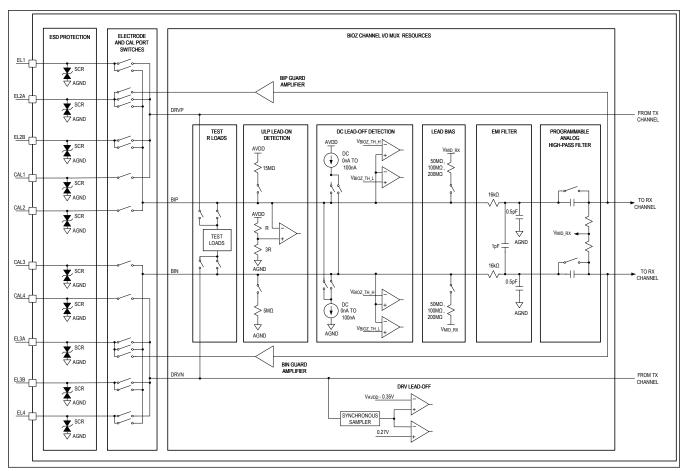

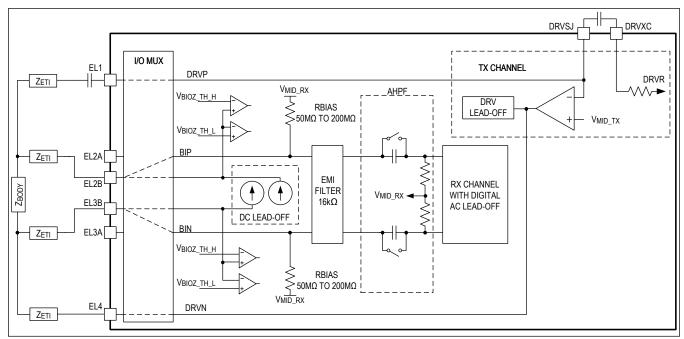

The MAX30009 is a complete Bioimpedance (BioZ) Analog Front-End (AFE) solution for wearable applications. It offers high performance for fitness, wellness, and clinical applications, and ultra-low power for long battery life. The BioZ receive channel has Electrostatic Discharge (ESD) protection, Electromagnetic Interference (EMI) filtering, internal lead-biasing, DC leads-off detection, DRVN lead-off detection, and ultra-low power lead-on detection during standby mode. The BioZ receive channel also has high input impedance, low noise, high Common-Mode Rejection Ratio (CMRR), programmable gain, various low-pass and high-pass filter options, and two high resolution analog-to-digital converters for simultaneous I and Q acquisition.

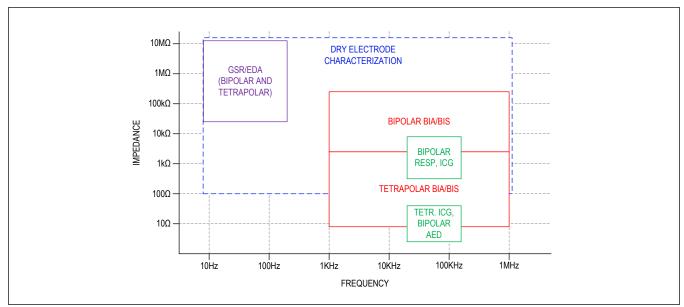

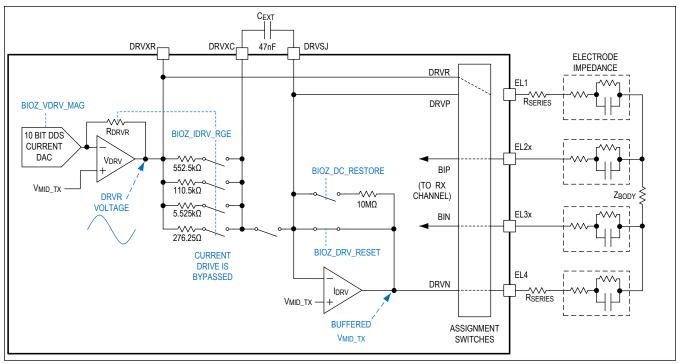

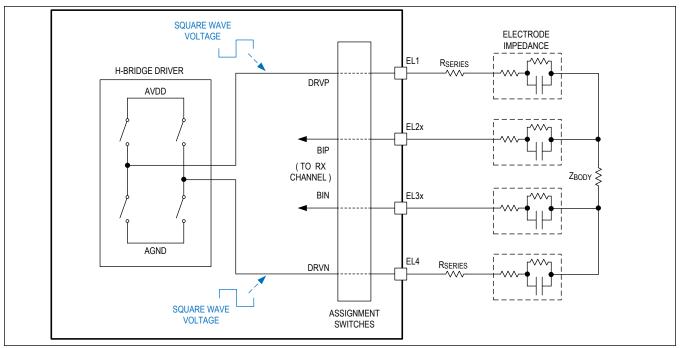

The BioZ transmit channel has a sine-wave current generator to drive AC currents into the body with a wide frequency range of 16Hz to 806kHz and a wide magnitude range of 16nA<sub>RMS</sub> to 1.28mA<sub>RMS</sub>. The transmit channel can also operate in the sine-wave voltage and H-bridge modes. The flexible input/output MUX allows for both bipolar and tetrapolar measurements with multiple sets of electrodes.

For measurements requiring high absolute impedance accuracy such as Bioimpedance Analysis/Spectroscopy (BIA/BIS) and Automated External Defibrillator (AED) body impedance, the MAX30009 offers several calibration options. An external precision resistor can be connected to the four-wire calibration port for the highest accuracy. Internal trimmed resistors also provide high accuracy.

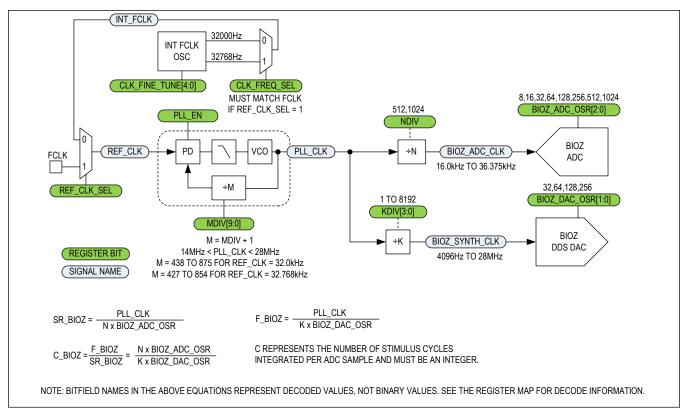

The PLL-based timing subsystem allows for a wide range of fine-tuned stimulus and sampling frequencies, and can be synchronized with other Analog Devices biosensors for simultaneous data collection.

The MAX30009 is available in a 2.03mm x 2.03mm, 25-bump Wafer-Level Package (WLP), operating over the -40°C to +85°C temperature range.

### **Applications**

- Wearable Fitness, Wellness, and Medical Devices

- Multifrequency Body Composition Analyzers

- Non-Invasive Hemodynamic Monitors

- Automatic External Defibrillators

- Optimized Performance to Accurately Detect:

- Respiration Rate

- · Galvanic Skin Response/Electrodermal Activity

- Bioimpedance Spectroscopy

- · Body Composition and Fluid Analysis

- Impedance Cardiography and Plethysmography

### **Benefits and Features**

#### **BIOZ**

- Complete High-Performance BioZ AFE

- Simultaneous I and Q Measurement Capability

- Four-Electrode (Tetrapolar) and Two-Electrode (Bipolar) Configurations

- Ultra-Low Power Operation

- 250 µW at 1.8V AVDD

- High-Resolution, 20-Bit Sigma Delta Analog-to-Digital Converters (ADCs)

- Wide Range of Sample Rates from 16sps to 4ksps

- Flexible and Programmable Input/Output MUX

- Low-Noise, High-Resolution Receive Channel

- 17 Bits Effective Resolution with 1.1μV<sub>P-P</sub> Noise

- High Input Impedance > 1GΩ for Extremely Low Common to Differential-Mode Conversion

- Programmable Sine-Wave Stimulus

- Low Frequency, Low Current Options for Galvanic Skin Response (GSR)/Electrodermal Activity (EDA) Starting from 16Hz and 16nA<sub>RMS</sub>

- Wide Range of Bioelectrical Impedance Analysis/ Spectroscopy (BIA/BIS) Frequencies from 1kHz to 806kHz

- High Currents at High Frequencies for Impedance Cardiography (ICG) Applications (e.g.,1.28mA<sub>RMS</sub> at 100kHz) with Lockout for Lower Frequencies for Conformance with 60601-1

- High Input AC Dynamic Range of >1000mV<sub>P-P</sub>

- 4-Pin In-Situ Calibration Port (4-Wire Precision Resistor) Enables High-Quality Absolute Impedance Measurements

- DC Leads-Off Detect Capability

- Ultra-Low Power Lead-On Detection with Interrupt for System Wake-Up.

- Lead-On Detect Current: 0.7µA (typ)

### **SYSTEM**

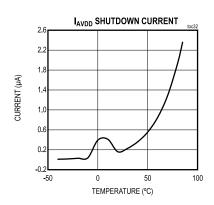

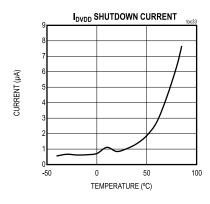

- Shutdown Current of 0.6µA (Typ)

- 256 Word FIFO

- Flexible PLL-Based Timing Subsystem with Internal or External Clock Source

- PLL can be Synchronized with Adjacent Biosensor AFEs (such as the MAX86176 Photoplethsymography (PPG)/Electrocardiography (ECG) AFE)

- Configurable Interrupts Reduce μC Wake-Up Time and Save Power

- High-Speed Serial Peripheral Interface (SPI) and I<sup>2</sup>C Digital Interface

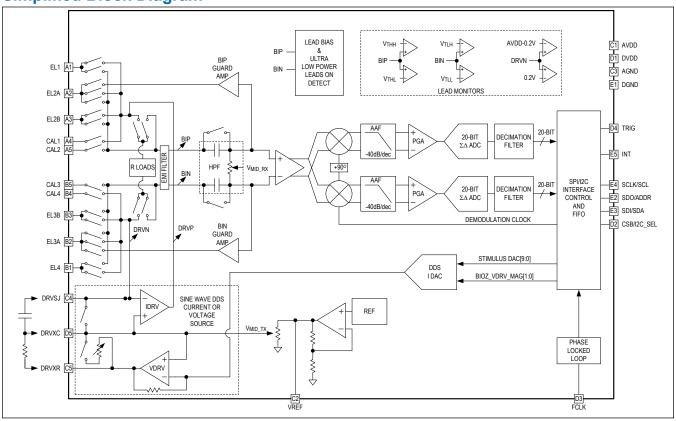

# **Simplified Block Diagram**

# Low-Power, High-Performance Bioimpedance Analog Front-End

### **TABLE OF CONTENTS**

| General Description.                                       |    |

|------------------------------------------------------------|----|

| Applications                                               | 1  |

| Benefits and Features                                      | 1  |

| Simplified Block Diagram                                   | 2  |

| Absolute Maximum Ratings                                   | 7  |

| Package Information                                        | 7  |

| WLP                                                        | 7  |

| Electrical Characteristics                                 | 7  |

| Typical Operating Characteristics                          | 16 |

| Pin Configuration                                          | 20 |

| WLP                                                        | 20 |

| Pin Description                                            | 20 |

| Detailed Description                                       | 22 |

| Timing Subsystem                                           | 22 |

| Clock Sources                                              | 23 |

| Phase-Locked Loop (PLL) and PLL Synchronization            | 23 |

| Sequence of Operation When PLL is Used                     | 24 |

| Enabling and Disabling the PLL                             | 24 |

| Entering and Exiting Shutdown                              | 24 |

| Soft-Reset Sequence                                        | 24 |

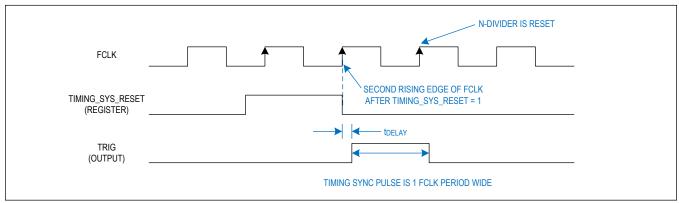

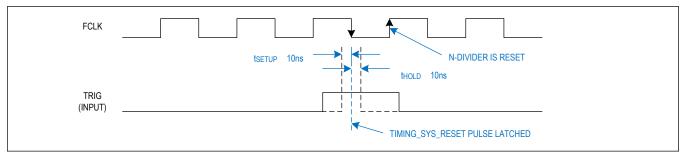

| PLL Synchronization                                        | 24 |

| PLL Synchronization Using the TRIG Pin                     | 24 |

| PLL Synchronization Using the Broadcast Command            | 26 |

| BioZ Sample Rate and Stimulus Frequency                    | 27 |

| FIFO Description                                           | 31 |

| BioZ                                                       | 31 |

| BioZ Start-up and Shutdown                                 | 33 |

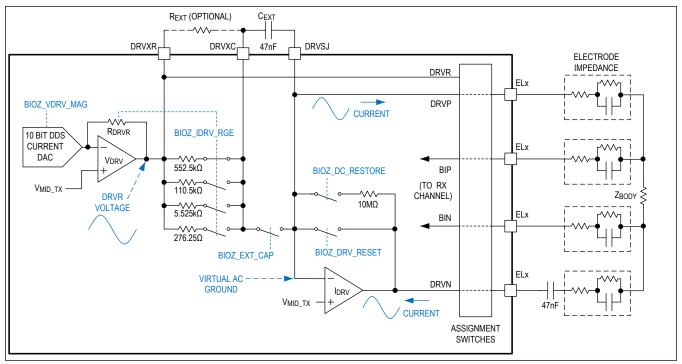

| BioZ Transmit Channel                                      | 33 |

| Sine-Wave Current Stimulus                                 | 33 |

| Sine-Wave Voltage Stimulus                                 |    |

| Square-Wave Voltage (H-Bridge) Stimulus                    | 36 |

| BioZ Receive Channel                                       | 37 |

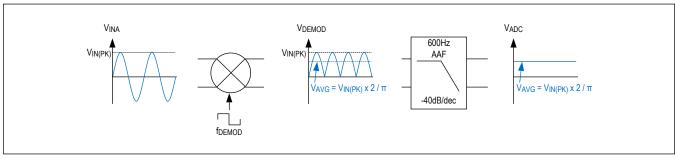

| BioZ Decimation and Digital Filters                        | 38 |

| Converting Digitized BioZ Samples to Voltage and Impedance | 38 |

| BioZ Noise Measurements                                    | 39 |

| BioZ Input/Output MUX                                      | 40 |

| BioZ EMI Filtering and ESD Protection                      | 41 |

| BioZ Lead Bias                                             | 41 |

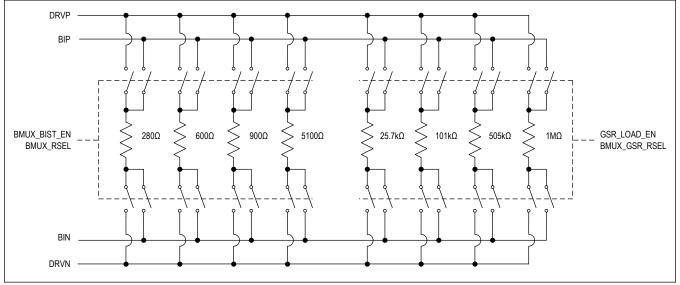

| Programmable BioZ Resistor Load                            | 42 |

## **TABLE OF CONTENTS (CONTINUED)**

| , ,                                                                                    |      |

|----------------------------------------------------------------------------------------|------|

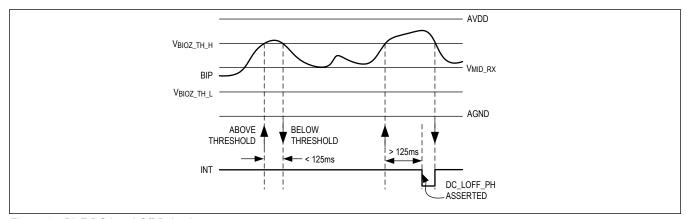

| BioZ Lead-Off Detection                                                                | . 42 |

| BioZ Ultra-Low-Power (ULP) Lead-On Detection                                           | . 45 |

| BioZ Calibration                                                                       | . 46 |

| Improving Accuracy of BIA/BIS Measurements                                             | . 48 |

| Digital Interface                                                                      | 49   |

| Serial Peripheral Interface (SPI)                                                      | 49   |

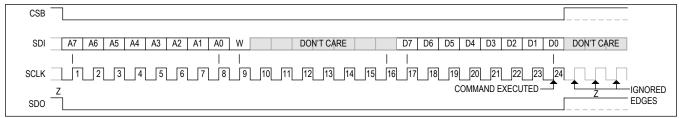

| Single-Word SPI Register Read and Write Transactions                                   | 49   |

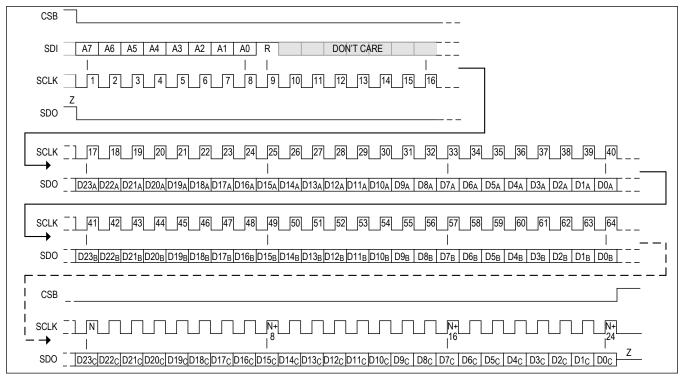

| SPI Burst-Mode Read Transaction                                                        | . 50 |

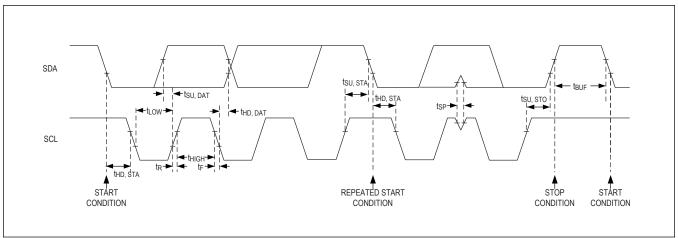

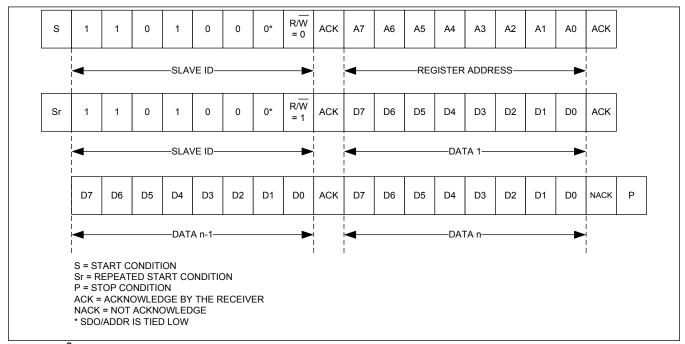

| I <sup>2</sup> C-/SMBus-Compatible Serial Interface                                    | . 51 |

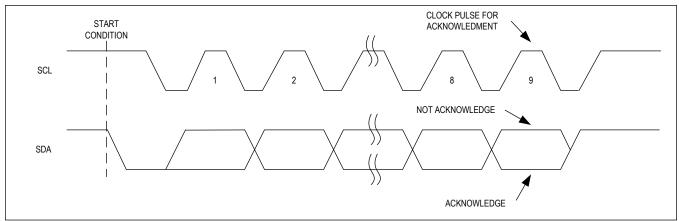

| Bit Transfer                                                                           | . 52 |

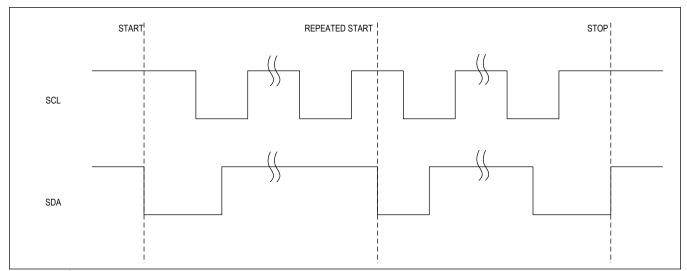

| START and STOP Conditions                                                              | . 52 |

| I <sup>2</sup> C Slave Address                                                         | . 53 |

| Acknowledge Bit                                                                        | . 53 |

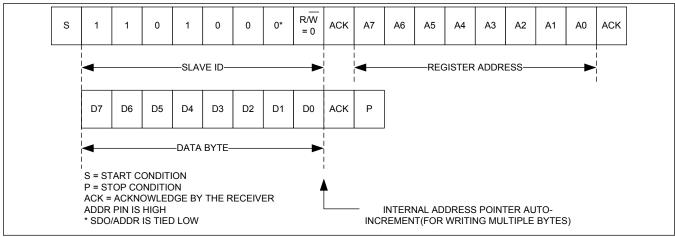

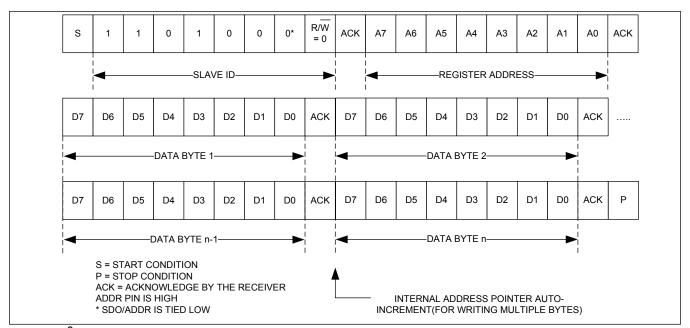

| I <sup>2</sup> C Write Data Format                                                     | . 54 |

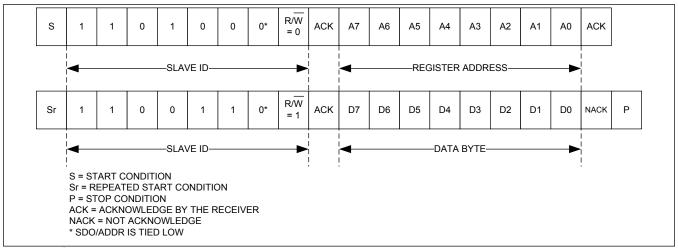

| I <sup>2</sup> C Read Data Format                                                      | . 55 |

| I <sup>2</sup> C Broadcast                                                             | . 56 |

| Register Map                                                                           | . 58 |

| User Register Map                                                                      | . 58 |

| Register Details                                                                       | . 60 |

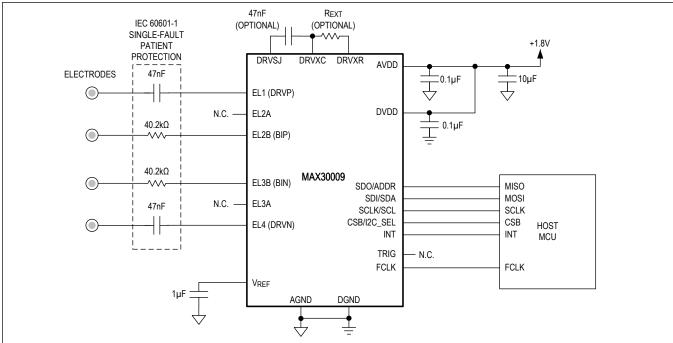

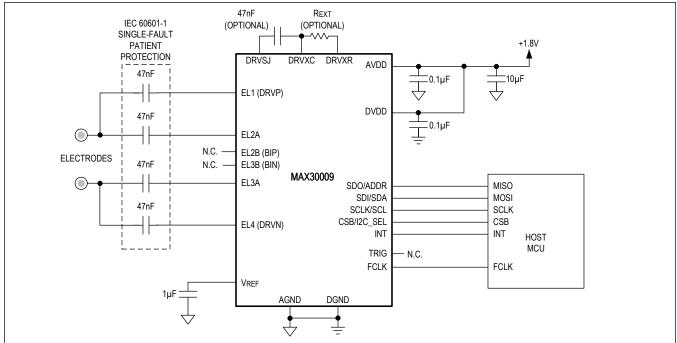

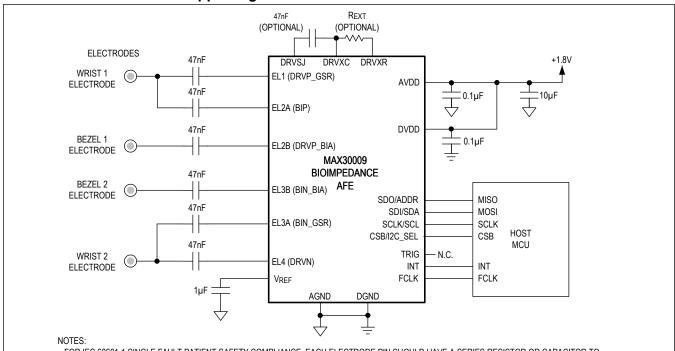

| Applications Information                                                               | . 89 |

| Patient Safety                                                                         | . 89 |

| Typical Application Circuits                                                           |      |

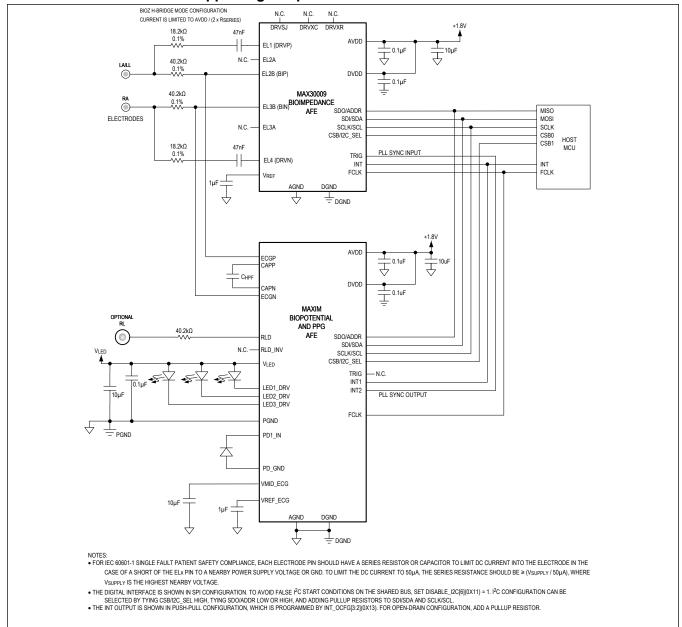

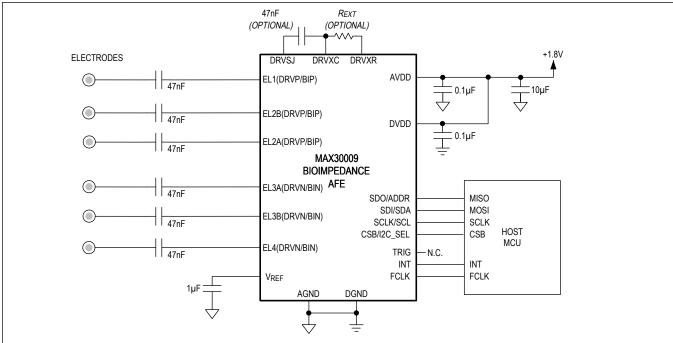

| 4-Electrode Device Supporting BIA/BIS, Respiration, or ICG                             | . 90 |

| 2-Electrode Device Supporting GSR/EDA                                                  | . 91 |

| 4-Electrode Wrist Device Supporting BIA and GSR                                        | . 92 |

| 2-Electrode Chest Device Supporting Respiration with ECG and PPG                       | . 93 |

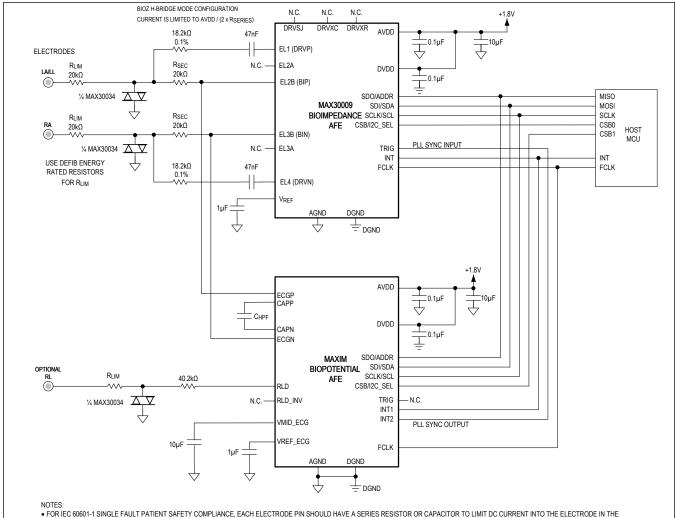

| 2-Electrode Chest Device Supporting Respiration with ECG and Defibrillation Protection | . 94 |

| 6-Electrode Device Supporting Multiple Measurement Vectors                             | . 95 |

| Ordering Information                                                                   | . 95 |

| Revision History                                                                       | . 96 |

# Low-Power, High-Performance Bioimpedance Analog Front-End

### LIST OF FIGURES

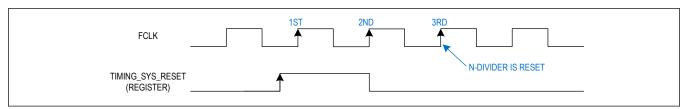

| Figure 1. Timing Subsystem                                                                | 23 |

|-------------------------------------------------------------------------------------------|----|

| Figure 2. Timing System Synchronization with MAX30009 as a Master                         | 25 |

| Figure 3. Timing System Synchronization with MAX30009 as a Slave                          | 26 |

| Figure 4. Timing System Synchronization for MAX30009 Using the Broadcast Feature          | 27 |

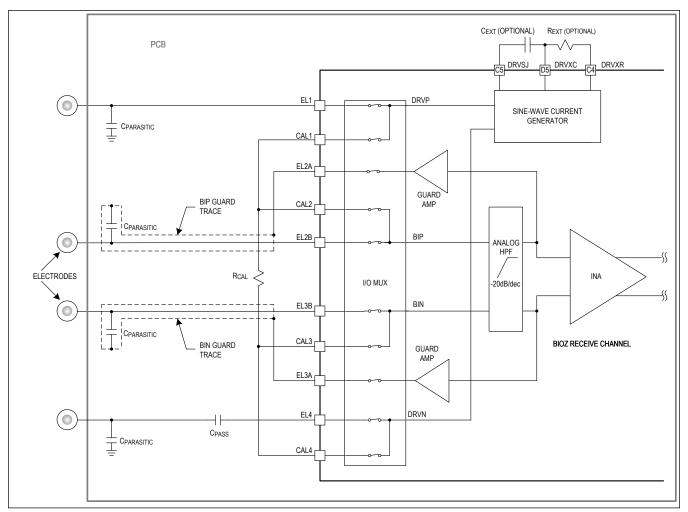

| Figure 5. BioZ System Block Diagram                                                       | 32 |

| Figure 6. BioZ Typical Application Areas                                                  | 33 |

| Figure 7. Bioimpedance Stimulus Generator — Sine-Wave Current Mode                        | 35 |

| Figure 8. Bioimpedance Stimulus Generator — Sine-Wave Voltage Mode                        | 36 |

| Figure 9. Bioimpedance Stimulus Generator — H-Bridge Square-Wave Voltage Mode             | 37 |

| Figure 10. BioZ Receive Channel                                                           | 38 |

| Figure 11. Square-Wave Demodulation for a Sine-Wave Stimulus (INA and PGA Gain Not Shown) | 39 |

| Figure 12. BioZ Input/Output MUX                                                          | 41 |

| Figure 13. Programmable Resistor Load                                                     | 42 |

| Figure 14. BioZ DC Lead-Off Behavior                                                      | 44 |

| Figure 15. BioZ DC Lead-Off Detection with Internal Sense                                 | 45 |

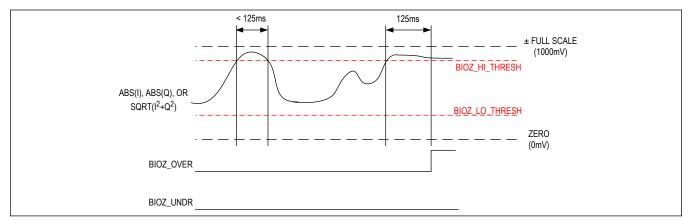

| Figure 16. BioZ Threshold Behavior                                                        | 45 |

| Figure 17. Calibration Port Connections                                                   | 48 |

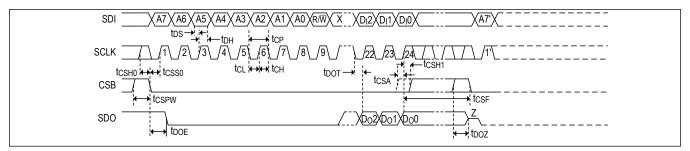

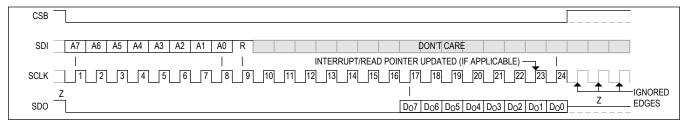

| Figure 18. Detailed SPI Timing Diagram                                                    | 49 |

| Figure 19. SPI Write Transaction                                                          | 50 |

| Figure 20. SPI Read Transaction                                                           | 50 |

| Figure 21. SPI FIFO Burst Mode Read Transaction                                           | 51 |

| Figure 22. Detailed I <sup>2</sup> C Timing Diagram                                       | 52 |

| Figure 23. I <sup>2</sup> C START, STOP, and REPEATED START Conditions                    | 53 |

| Figure 24. I <sup>2</sup> C Acknowledge Bit                                               | 54 |

| Figure 25. I <sup>2</sup> C Single-Byte Write Transaction                                 | 54 |

| Figure 26. I <sup>2</sup> C Multibyte Write Transaction                                   | 55 |

| Figure 27. I <sup>2</sup> C Single-Byte Read Transaction                                  |    |

| Figure 28, I2C Multibyte Read Transaction                                                 | 56 |

# MAX30009

# Low-Power, High-Performance Bioimpedance Analog Front-End

## LIST OF TABLES

| Table 1. Example Calculations of BioZ Configuration Parameters for F_BIOZ < 54688Hz | 28 |

|-------------------------------------------------------------------------------------|----|

| Table 2. Example Calculations of BioZ Configuration Parameters for F_BIOZ > 54688Hz | 28 |

| Table 3. Common BioZ Stimulus Frequencies and Sample Rates with REF_CLK = 32.768kHz | 29 |

| Table 4. FIFO Data Format                                                           | 31 |

| Table 5. Stimulus Current Options                                                   | 34 |

| Table 6. BioZ Receive Channel Input-Referred Noise, 256sps                          | 39 |

| Table 7. Input-Referred Noise Frequency Settings                                    | 40 |

| Table 8. BioZ Lead-Off Cases                                                        | 43 |

| Table 9. I <sup>2</sup> C Addresses for MAX30009                                    | 53 |

| Table 10. Allowed Current Magnitudes vs. Frequency                                  | 89 |

# Low-Power, High-Performance Bioimpedance Analog Front-End

### **Absolute Maximum Ratings**

| AVDD to AGND0.3V to +2.2V                           | All Other Pins to AGND0.3V to +2.2V       |

|-----------------------------------------------------|-------------------------------------------|

| DVDD to DGND0.3V to +2.2V                           | Maximum Current into Any Pin±50mA         |

| AVDD to DVDD0.3V to +0.3V                           | Operating Temperature Range40°C to +85°C  |

| DGND to AGND0.3V to +0.3V                           | Junction Temperature+150°C                |

| SDI/SDA, SCLK/SCL, CSB/I2C_SEL to DGND0.3V to +5.5V | Storage Temperature Range65°C to +150°C   |

| SDO/ADDR to DGND                                    | Lead Temperature (Soldering, 10sec)+300°C |

| INT, TRIG to DGND0.3V to +5.5V                      | Soldering Temperature (Reflow)+260°C      |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

### **WLP**

| Package Code                           | N252C2+1                       |

|----------------------------------------|--------------------------------|

| Outline Number                         | <u>21-100494</u>               |

| Land Pattern Number                    | Refer to Application Note 1891 |

| Thermal Resistance, Four-Layer Board:  |                                |

| Junction-to-Ambient (θ <sub>JA</sub> ) | 52.43°C/W                      |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

### **Electrical Characteristics**

(AVDD = 1.8V, DVDD = 1.8V, FCLK = 32.768Hz,  $T_A$  = +25°C, min/max are from  $T_A$  = -40°C to +85°C, unless otherwise noted, <u>Note 1</u>)

| PARAMETER                             | SYMBOL      | CONDITIONS                                                                                                                                                            | MIN   | TYP           | MAX   | UNITS |

|---------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------|-------|-------|

| BIOZ Characteristics / R              | eceive Path |                                                                                                                                                                       |       |               |       |       |

| ADC Resolution                        |             |                                                                                                                                                                       |       | 20            |       | bits  |

| ENOB                                  |             | BIOZ_ADC_OSR = 128                                                                                                                                                    |       | 16.3          |       | bits  |

| ENOD                                  | NOD .       | BIOZ_ADC_OSR = 8                                                                                                                                                      |       | 9.6           |       | Dits  |

| ADC Sample Rate                       |             | Programmable, see <u>Timing Subsystem</u>                                                                                                                             |       | 16 to<br>4546 |       | sps   |

| Phase Measurement                     |             | Cole Impedance (324 $\Omega$    ( 232 $\Omega$ + 22nF)) load at 50kHz after calibration, TA = +25°C. ( <i>Note 2</i> , <i>Note 3</i> )                                | -0.15 |               | +0.15 | 4     |

| Accuracy at 50kHz                     |             | Cole Impedance ( $800\Omega \parallel$ ( $2500\Omega + 1nF$ )) load at 50kHz after calibration, TA = +25°C. ( <u>Note 2</u> , <u>Note 3</u> )                         | -0.1  |               | +0.1  | deg   |

| Phase Measurement<br>Accuracy at 16Hz |             | 453kΩ in series with 22nF load at 16Hz after calibration ( $Note\ 2$ ), $T_A = +25^{\circ}C$ . BIOZ_DC_RESTORE feedback resistance enabled in parallel with the load. |       | ±1            |       | deg   |

(AVDD = 1.8V, DVDD = 1.8V, FCLK = 32.768Hz,  $T_A$  = +25°C, min/max are from  $T_A$  = -40°C to +85°C, unless otherwise noted, <u>Note 1</u>)

| PARAMETER                                      | SYMBOL | CONDITIONS                                                                                                                                                               | MIN  | TYP     | MAX  | UNITS             |

|------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|------|-------------------|

| Phase Measurement<br>Accuracy at 500kHz        |        | 316Ω in series with 1nF load at 500kHz after calibration ( $Note\ 2$ ), $T_A = +25$ °C.                                                                                  |      | ±1      |      | deg               |

| Phase Measurement<br>Drift                     |        | Drift of impedance phase at 50kHz after calibration ( $Note\ 2$ ), drift relative to $T_A = +25^{\circ}C$ .                                                              |      | ±0.003  |      | deg/°C            |

| Magnitude<br>Measurement Accuracy              |        | Cole Impedance (324 $\Omega$    (232 $\Omega$ + 22nF)) load at 50kHz after calibration, TA = +25°C. ( <i>Note 2</i> , <i>Note 3</i> )                                    | -0.1 |         | +0.1 | - %               |

| at 50kHz                                       |        | Cole Impedance ( $800\Omega$    ( $2500\Omega + 1nF$ )) load at 50kHz after calibration, TA = +25°C. ( <u>Note 2</u> , <u>Note 3</u> )                                   | -0.1 |         | +0.1 | 70                |

| Magnitude<br>Measurement Accuracy<br>at 16Hz   |        | 453kΩ in series with 22nF load at 16Hz after calibration ( $\underline{Note~2}$ ), $T_A$ = +25°C. BIOZ_DC_RESTORE feedback resistance enabled in parallel with the load. |      | ±1      |      | %                 |

| Magnitude<br>Measurement Accuracy<br>at 500kHz |        | 316Ω in series with 1nF load at 500kHz after calibration ( $\underline{Note\ 2}$ ), $T_A = +25$ °C.                                                                      |      | ±1      |      | %                 |

| Magnitude<br>Measurement Drift                 |        | Drift of impedance magnitude at 50kHz after calibration ( $Note\ 2$ ), drift relative to $T_A = +25$ °C                                                                  |      | ±0.017  |      | %/°C              |

|                                                |        | $R_{BODY}$ = 100kΩ, conditions for GSR (Note 4)                                                                                                                          |      | 2.53    |      | $\Omega_{RMS}$    |

| Impedance<br>Repeatability                     |        | $R_{BODY}$ = 680Ω, conditions for respiration ( <i>Note 4</i> )                                                                                                          |      | 8.94    |      | 0                 |

|                                                |        | $R_{BODY}$ = 25Ω, conditions for ICG/AED body impedance ( <i>Note 4</i> )                                                                                                |      | 0.80    |      | mΩ <sub>RMS</sub> |

| DC Power Supply                                | PSRR   | $I_{DRV}$ = 64 $\mu$ A <sub>RMS</sub> , F_BIOZ = 1kHz,<br>BIOZ_GAIN = 10V/V, R <sub>BODY</sub> = 1k $\Omega$ ,<br>V <sub>AVDD</sub> = V <sub>DVDD</sub> = 1.7V to 2.0V   |      | 900     | 7000 | - LSB/V           |

| Rejection                                      | FORK   | V <sub>DRV</sub> = 100mV <sub>P-P</sub> , F_BIOZ = 64Hz,<br>BIOZ_GAIN = 10V/V, V <sub>AVDD</sub> = V <sub>DVDD</sub> =<br>1.7V to 2.0V                                   |      | 150     | 1800 | LSB/V             |

| Channel Gain                                   |        | Selected by BIOZ_GAIN                                                                                                                                                    |      | 1 to 10 |      | V/V               |

| I vs. Q Channel Gain<br>Matching               |        | $3\sigma$ with Cole Impedance (324Ω    232Ω-22nF) load at 50kHz after calibration, TA = +25°C. ( <i>Note 2</i> )                                                         |      | 0.2     |      | %                 |

| AC Differential Input<br>Signal                |        | Shift from small-signal gain < 0.6%,<br>BIOZ_GAIN = 1V/V, f <sub>IN</sub> = 1kHz                                                                                         |      |         | 1000 | mV <sub>P-P</sub> |

| Input Referred Voltage<br>Noise (BIP, BIN)     |        | Integrated Noise BW = 0.05 to 100Hz,<br>Gain = 10x, Current Drive Off, BIN = BIP<br>= VCM                                                                                |      | 1.0     |      | μV <sub>RMS</sub> |

| Input Referred Current<br>Noise                |        | DRVP and DRVN Disconnected, BIOZ_GAIN = 10V/V, F_BIOZ = 65.5kHz, SR_BIOZ = 256sps, BIOZ_DLPF = 64Hz, 200MΩ Lead Bias, BIOZ_AHPF = 5kHz                                   |      | 300     |      | fA/√Hz            |

(AVDD = 1.8V, DVDD = 1.8V, FCLK = 32.768Hz,  $T_A$  = +25°C, min/max are from  $T_A$  = -40°C to +85°C, unless otherwise noted, <u>Note 1</u>)

| PARAMETER                                     | SYMBOL              | CONDITIONS                                                                                                                                           | MIN   | TYP              | MAX  | UNITS             |

|-----------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|------|-------------------|

| Input Referred Offset<br>Voltage              |                     | $R_{BODY} = 0\Omega$ , BIOZ_GAIN = 10V/V, BIOZ_AHPF = Bypass, Demodulation Disabled                                                                  | -6    |                  | +6   | mV                |

| Differential Input                            |                     | Lead bias disabled, BIOZ_AHPF = 100Hz                                                                                                                |       | 48               |      | ΜΩ                |

| Differential Input<br>Impedance               |                     | Lead bias disabled, BIOZ_AHPF = bypass                                                                                                               |       | 10GΩ//2<br>pF    |      |                   |

| Common-Mode Input Impedance                   |                     | Lead bias disabled, BIOZ_AHPF = bypass                                                                                                               |       | 3GΩ/2pF          |      |                   |

| Input Analog High-Pass<br>Filter              |                     | Programmable, see Register Map.                                                                                                                      |       | 100 to<br>10,000 |      | Hz                |

| Input Analog High-Pass<br>Filter Variation    |                     |                                                                                                                                                      | -50   |                  | +100 | %                 |

|                                               |                     | BIOZ_AHPF[3:0] = 1000                                                                                                                                | 14    | 24               | 36   |                   |

|                                               |                     | BIOZ_AHPF[3:0] = 1001                                                                                                                                | 7     | 12               | 18   | MΩ                |

| Input Analog High-Pass                        |                     | BIOZ_AHPF[3:0] = 1010                                                                                                                                | 2.6   | 4.8              | 7    |                   |

| Filter Resistor                               |                     | BIOZ_AHPF[3:0] = 1011                                                                                                                                | 1.3   | 2.4              | 3.3  |                   |

|                                               |                     | BIOZ_AHPF[3:0] = 1100                                                                                                                                | 0.75  | 1.1              | 1.5  |                   |

|                                               |                     | BIOZ_AHPF[3:0] = 1101 or 1110                                                                                                                        | 0.3   | 0.47             | 0.65 |                   |

| Input Analog High-Pass<br>Filter Bias Voltage | V <sub>MID_RX</sub> |                                                                                                                                                      | 0.79  | 0.81             | 0.83 | V                 |

| Input Leakage Current                         |                     | BIP, BIN = V <sub>AVDD</sub> - 0.2V or AGND + 0.2V, TA = +25°C                                                                                       | -3    | 0.1              | +3   | nA                |

| I/Q Gain Matching                             |                     | 1kHz input, I/Q correlated with same phase, $T_A$ = +25°C, 1 $\sigma$                                                                                |       | 0.2              |      | %                 |

| BIOZ Characteristics / Tr                     | ansmit Path         |                                                                                                                                                      |       |                  |      |                   |

| DDS Sine-Wave<br>Resolution                   |                     |                                                                                                                                                      |       | 10               |      | bits              |

| Current-Drive Amplitude Resolution            |                     | See BIOZ_VDRV_MAG[1:0] and BIOZ_IDRV_RGE[1:0]                                                                                                        |       | 4                |      | bits              |

| Current-Drive Range 0                         |                     | BIOZ_IDRV_RGE[1:0] = 0x0, sine-wave drive with amplitude = 16nA <sub>RMS</sub> , 32nA <sub>RMS</sub> , 80nA <sub>RMS</sub> , 160nA <sub>RMS</sub>    | 16    |                  | 160  | nA <sub>RMS</sub> |

| Current-Drive Range 1                         |                     | BIOZ_IDRV_RGE[1:0] = 0x1, sine-wave drive with amplitude = 320nA <sub>RMS</sub> , 640nA <sub>RMS</sub> , 1.6μA <sub>RMS</sub> , 3.2μA <sub>RMS</sub> | 0.32  |                  | 3.2  | μA <sub>RMS</sub> |

| Current-Drive Range 2                         |                     | BIOZ_IDRV_RGE[1:0] = 0x2, sine-wave drive with amplitude = $6.4\mu A_{RMS}$ , $12.8\mu A_{RMS}$ , $32\mu A_{RMS}$ , $64\mu A_{RMS}$                  | 6.4   |                  | 64   | μA <sub>RMS</sub> |

| Current-Drive Range 3                         |                     | BIOZ_IDRV_RGE[1:0] = 0x3, sine-wave with amplitude = $128\mu A_{RMS}$ , $256\mu A_{RMS}$ , $640\mu A_{RMS}$ , $1.28m A_{RMS}$                        | 0.128 |                  | 1.28 | mA <sub>RMS</sub> |

|                                               |                     | BIOZ_DRV_MODE[1:0] = Voltage Mode, DRVP, DRVN shorted to AVDD, AGND                                                                                  | 0.8   | 1.5              | 3    |                   |

| Short-Circuit Current                         |                     | BIOZ_DRV_MODE[1:0] = H-Bridge<br>Mode, DRVP, DRVN shorted to AVDD,<br>AGND                                                                           | 2.0   | 3.5              | 6.0  | mA                |

(AVDD = 1.8V, DVDD = 1.8V, FCLK = 32.768Hz,  $T_A$  = +25°C, min/max are from  $T_A$  = -40°C to +85°C, unless otherwise noted, <u>Note 1</u>)

| PARAMETER                                           | SYMBOL                              | CONDITIONS                                                                                                                  | MIN                      | TYP                               | MAX                         | UNITS  |

|-----------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------|-----------------------------|--------|

| Comment Daise Assume                                |                                     | I <sub>DRV</sub> ≥ 32nA <sub>RMS</sub>                                                                                      | -6                       |                                   | +6                          | 0/     |

| Current-Drive Accuracy                              |                                     | I <sub>DRV</sub> = 16nA <sub>RMS</sub>                                                                                      | -10                      |                                   | +10                         | %      |

| Current-Drive Total<br>Harmonic Distortion<br>(THD) |                                     | $I_{DRV}$ = 64μA <sub>RMS</sub> , f <sub>STIM</sub> = 50kHz, R <sub>BODY</sub> = 1kΩ. Include odd harmonics h3, h5, and h7. |                          | 0.07                              | 0.3                         | %      |

| Current-Drive<br>Temperature Coefficient            |                                     |                                                                                                                             |                          | 128                               |                             | ppm/°C |

| Current-Drive Power Supply Rejection                |                                     | I <sub>DRV</sub> = 64μA, DC test mode                                                                                       |                          | 0.1                               |                             | %/V    |

| Compliance Voltage                                  |                                     | BIOZ_DRV_MODE[1:0] = current mode, current accuracy ±1%                                                                     | 0.2                      |                                   | V <sub>AVDD</sub> - 0.2     | V      |

| Compliance Monitor<br>Thresholds                    |                                     | EN_DRV_OOR = 1                                                                                                              | 0.27                     |                                   | V <sub>AVDD</sub> -<br>0.35 | V      |

| Drive Frequency Range                               |                                     | See BIOZ_FREQ_DIV[3:0]                                                                                                      |                          | 0.016 to<br>500                   |                             | kHz    |

| Drive Common-Mode<br>Voltage                        | V <sub>MID_TX</sub>                 | Voltage at DRVSJ in current mode                                                                                            | 0.79                     | 0.81                              | 0.83                        | V      |

| <b>BIOZ Characteristics / D</b>                     | igital Filter                       |                                                                                                                             |                          |                                   |                             |        |

| Output Digital Low-Pass                             |                                     | BIOZ_DLPF[2:0] = 0x1                                                                                                        |                          | 0.005 x<br>SR_BIO<br>Z            |                             |        |

|                                                     |                                     | BIOZ_DLPF[2:0] = 0x2                                                                                                        |                          | 0.02 x<br>SR_BIO<br>Z             |                             |        |

| Filter                                              |                                     | BIOZ_DLPF[2:0] = 0x3                                                                                                        |                          | 0.08 x<br>SR_BIO<br>Z             |                             | Hz     |

|                                                     |                                     | BIOZ_DLPF[2:0] ≥ 0x4                                                                                                        |                          | 0.25 x<br>SR_BIO<br>Z             |                             |        |

| Output Digital High-Pass                            |                                     | BIOZ_DHPF[1:0] = 0x1                                                                                                        |                          | 0.00025<br>x<br>SR_BIO<br>Z       |                             | Hz     |

| Filter                                              |                                     | BIOZ_DHPF[1:0] ≥ 0x2                                                                                                        |                          | 0.002 x<br>SR_BIO<br>Z            |                             |        |

| BIOZ I/O Mux / DC Leads                             | Off                                 |                                                                                                                             | •                        |                                   |                             | •      |

| Full-Scale Current                                  |                                     | Selected by LOFF_IMAG[2:0]                                                                                                  |                          | 5.5,<br>11.3,<br>22.5, 55,<br>110 |                             | nA     |

| Full-Scale Current<br>Accuracy                      |                                     | LOFF_IMAG = 110nA                                                                                                           | -40                      |                                   | +40                         | %      |

| Comparator Threshold                                | V <sub>THH</sub> , V <sub>THL</sub> | Selectable by DC_LOFF_THRESH[3:0]                                                                                           | V <sub>MID</sub><br>±200 |                                   | V <sub>MID</sub><br>±695    | mV     |

(AVDD = 1.8V, DVDD = 1.8V, FCLK = 32.768Hz,  $T_A$  = +25°C, min/max are from  $T_A$  = -40°C to +85°C, unless otherwise noted, <u>Note 1</u>)

| PARAMETER                                    | SYMBOL              | COND                                                        | ITIONS                             | MIN                           | TYP                          | MAX   | UNITS             |

|----------------------------------------------|---------------------|-------------------------------------------------------------|------------------------------------|-------------------------------|------------------------------|-------|-------------------|

| Comparator Threshold<br>Accuracy             |                     | LOFF_THRESH = V                                             | MID_RX ± 425mV                     | -5                            |                              | +5    | %                 |

| Full-Scale Electrode                         |                     | LOFF_IMAG = 100n<br>V <sub>MID_RX</sub> ± 210mV             | A, LOFF_THRESH =                   |                               | 4                            |       | - ΜΩ              |

| Resistance                                   |                     | LOFF_IMAG = 10nA, LOFF_THRESH = V <sub>MID_RX</sub> ± 660mV |                                    |                               | 100                          |       | 10177             |

| BIOZ I/O Mux / Lead Bias                     | ;                   |                                                             |                                    |                               |                              |       | •                 |

|                                              |                     |                                                             | RBIAS_VALUE = 0x0                  |                               | 50                           |       |                   |

| Lead Bias Impedance                          |                     | Lead bias eriabled. 0                                       | RBIAS_VALUE = 0x1                  |                               | 100                          |       | ΜΩ                |

|                                              |                     |                                                             | RBIAS_VALUE = 0x2                  |                               | 200                          |       |                   |

| Lead Bias Voltage                            |                     | Lead bias enabled                                           |                                    | 0.76                          | 0.81                         | 0.84  | V                 |

| BIOZ I/O Mux / Internal R                    | esisitive Loads     | 3                                                           |                                    |                               |                              |       | •                 |

| Internal BIA Resistive<br>Load Nominal Value | R <sub>VAL</sub>    | Selected by BMUX_                                           | Selected by BMUX_RSEL              |                               | 280,<br>600,<br>900,<br>5100 |       | Ω                 |

| Internal GSR Resistive<br>Load Nominal Value | R <sub>GSR</sub>    | Selected by BMUX_                                           |                                    | 25.7,<br>101,<br>505,100<br>0 |                              | kΩ    |                   |

| Timing Subsystem                             |                     |                                                             |                                    |                               |                              |       | 1                 |

| PLL Lock Time                                |                     | Change in FCLK to I asserted, MDIV = 0x                     |                                    |                               | 2                            | 5     | ms                |

| FCLK Input Frequency                         |                     | Must match CLK_FF                                           | REQ_SEL                            |                               | 32.0 or<br>32.768            |       | kHz               |

| Maximum FCLK Rise<br>Time (10% to 90%)       | tRISE               | T <sub>A</sub> = +25°C, V <sub>IN</sub> = 0<br>15pF         | V or 1.8V, C <sub>LOAD</sub> =     |                               | 100                          |       | ns                |

| Maximum FCLK Fall<br>Time (90% to 10%)       | t <sub>FALL</sub>   | T <sub>A</sub> = +25°C, V <sub>IN</sub> = 0°<br>15pF        | V or 1.8V, C <sub>LOAD</sub> =     |                               | 100                          |       | ns                |

| PLL External Reference<br>Jitter             |                     | Cycle-to-cycle period PLL_LOCK_WNDW                         |                                    |                               | 3                            |       | ns <sub>RMS</sub> |

|                                              |                     | CLK FREQ SEL =                                              | T <sub>A</sub> = 25°C              | -1                            | ±0.4                         | +1    |                   |

| Internal FCLK                                | FCLK <sub>INT</sub> | 32.0kHz                                                     | T <sub>A</sub> = -40°C to<br>+85°C | -2.5                          | ±0.4                         | +2.5  | %                 |

| IIIICIIIAI FOLK                              |                     | CLK EDEO OF                                                 | T <sub>A</sub> = 25°C              | -1                            | ±0.4                         | +1    | 70                |

|                                              | FLCK <sub>INT</sub> | CLK_FREQ_SEL = 32.768kHz                                    | T <sub>A</sub> = -40°C to<br>+85°C | -2.5                          | ±0.4                         | +2.5  |                   |

| Internal Reference                           |                     |                                                             |                                    |                               | <u> </u>                     |       |                   |

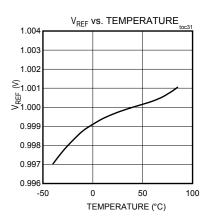

| Reference Output<br>Voltage                  | V <sub>REF</sub>    | TA = +25°C                                                  |                                    | 0.985                         | 1                            | 1.015 | V                 |

| Reference Temperature<br>Coefficient         | TC <sub>REF</sub>   |                                                             |                                    |                               | 42                           |       | ppm/°C            |

(AVDD = 1.8V, DVDD = 1.8V, FCLK = 32.768Hz,  $T_A$  = +25°C, min/max are from  $T_A$  = -40°C to +85°C, unless otherwise noted, <u>Note 1</u>)

| PARAMETER                                            | SYMBOL                                   | CONDITIONS                                                                                                                                                                                                                                                                                                 | MIN | TYP  | MAX  | UNITS |

|------------------------------------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|

| BIA Supply Current                                   |                                          |                                                                                                                                                                                                                                                                                                            |     |      |      | •     |

| V <sub>AVDD</sub> Supply Voltage                     | V <sub>AVDD</sub>                        | Verified during Power-Supply Rejection Ratio (PSRR) tests                                                                                                                                                                                                                                                  | 1.7 | 1.8  | 2.0  | V     |

| V <sub>DVDD</sub> Supply Voltage                     | V <sub>DVDD</sub>                        | Verified during Power-Supply Rejection Ratio (PSRR) tests                                                                                                                                                                                                                                                  | 1.7 | 1.8  | 2.0  | V     |

| BIA Supply Current<br>(BIA/BIS Example at<br>1KHz)   | I <sub>AVDD</sub> +<br>I <sub>DVDD</sub> | PLL_CLK = 16.384MHz, F_BIOZ = 1kHz (KDIV = 64, M = 500, FCLK = 32768Hz, BIOZ_DAC_OSR = 256); BIOZ_DRV_MODE = current; BIOZ_INA_MODE = low power; BIOZ_GAIN = 10V/V; SR_BIOZ = 62.5sps (NDIV = 512, BIOZ_ADC_OSR = 512); I <sub>MAG</sub> = 32µA; I and Q ADCs enabled; Digital filters bypassed            |     | 926  |      | μΑ    |

| BIA Supply Current<br>(BIA/BIS Example at<br>50KHz)  | I <sub>AVDD</sub> +<br>I <sub>DVDD</sub> | PLL_CLK = 25.591808MHz, F_BIOZ = 49.984kHz (KDIV = 2, M = 781, FCLK = 32768Hz, BIOZ_DAC_OSR = 256); BIOZ_DRV_MODE = current; BIOZ_INA_MODE = low noise; BIOZ_GAIN = 10V/V; SR_BIOZ = 48.8125sps (NDIV = 1024, BIOZ_ADC_OSR = 512); I <sub>MAG</sub> = 32µA; I and Q ADCs enabled; Digital filters bypassed |     | 1222 | 2700 | μΑ    |

| BIA Supply Current<br>(BIA/BIS Example at<br>100KHz) | I <sub>AVDD</sub> +<br>I <sub>DVDD</sub> | PLL_CLK = 25.591808MHz, F_BIOZ = 99.968kHz (KDIV=2, M = 781, FCLK = 32768Hz, BIOZ_DAC_OSR = 128); BIOZ_DRV_MODE = current; BIOZ_INA_MODE = low noise; BIOZ_GAIN = 10V/V; SR_BIOZ = 48.8125sps (NDIV = 1024, BIOZ_ADC_OSR = 512); I <sub>MAG</sub> = 32μA; I and Q ADCs enabled; Digital filters bypassed   |     | 1227 |      | μА    |

| BIA Supply Current<br>(BIA/BIS Example at<br>250KHz) | I <sub>AVDD</sub> +<br>I <sub>DVDD</sub> | PLL_CLK = 15.990784MHz, F_BIOZ = 249.856kHz (KDIV = 1, M = 488, FCLK = 32768Hz, BIOZ_DAC_OSR = 64); BIOZ_DRV_MODE = current; BIOZ_INA_MODE = low noise; BIOZ_GAIN = 10V/V; SR_BIOZ = 61sps (NDIV = 512, BIOZ_ADC_OSR = 512); I <sub>MAG</sub> = 32µA; I and Q ADCs enabled; Digital filters bypassed       |     | 1148 | 2700 | μА    |

| BIA Supply Current<br>(BIA/BIS Example at<br>500KHz) | I <sub>AVDD</sub> +<br>I <sub>DVDD</sub> | PLL_CLK = 15.990784MHz, F_BIOZ = 499.712kHz (KDIV = 1, M = 488, FCLK = 32768Hz, BIOZ_DAC_OSR = 32); BIOZ_DRV_MODE = current; BIOZ_INA_MODE = low noise; BIOZ_GAIN = 10V/V; SR_BIOZ = 61sps (NDIV = 512, BIOZ_ADC_OSR = 512); I <sub>MAG</sub> = 32µA; I and Q ADCs enabled; Digital filters bypassed       |     | 1192 |      | μА    |

(AVDD = 1.8V, DVDD = 1.8V, FCLK = 32.768Hz,  $T_A$  = +25°C, min/max are from  $T_A$  = -40°C to +85°C, unless otherwise noted, <u>Note 1</u>)

| PARAMETER                                                    | SYMBOL                                   | CONDITIONS                                                                                                                                                                                                                                                                                                                              | MIN | TYP  | MAX  | UNITS |

|--------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|

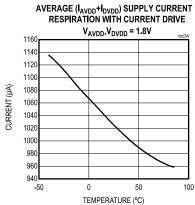

| BIA Supply Current<br>(Respiration Current<br>Drive Example) | IAVDD +<br>I <sub>DVDD</sub>             | PLL_CLK = 16.384MHz, F_BIOZ = 32kHz (KDIV = 2, M = 500, FCLK = 32768HZ, BIOZ_DAC_OSR = 256); BIOZ_DRV_MODE = current; BIOZ_INA_MODE = low power; BIOZ_GAIN = 10V/V; SR_BIOZ = 62.5sps (NDIV = 512, BIOZ_ADC_OSR = 512); I <sub>MAG</sub> = 32µA; In-phase ADC only; BIOZ_DHPF = bypass, BIOZ_DLPF = 0.08 x SR_BIOZ                      |     | 943  | 2300 | μА    |

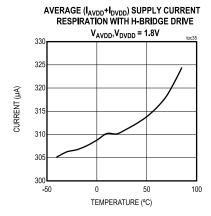

| BIA Supply Current<br>(Respiration H-Bridge<br>Example)      | IAVDD +<br>IDVDD                         | PLL_CLK = 16.384MHz, F_BIOZ = 32kHz (KDIV = 2, M = 500, FCLK = 32768Hz, BIOZ_DAC_OSR = 256); BIOZ_DRV_MODE = current; BIOZ_INA_MODE = low power; BIOZ_GAIN = 10V/V; SR_BIOZ = 62.5sps (NDIV = 512, BIOZ_ADC_OSR = 512); No load; In-phase ADC only; BIOZ_DHPF = bypass, BIOZ_DLPF = 0.08 x SR_BIOZ                                      |     | 328  |      | μΑ    |

| BIA Supply Current (ICG<br>Example)                          | I <sub>AVDD</sub> +<br>I <sub>DVDD</sub> | PLL_CLK = 25.591808MHz, F_BIOZ = 99.968kHz (KDIV = 1, M = 781, FCLK = 32768Hz, BIOZ_DAC_OSR = 256); BIOZ_DRV_MODE = current; BIOZ_INA_MODE = low noise; BIOZ_GAIN = 10V/V; SR_BIOZ = 97.625sps (NDIV = 1024, BIOZ_ADC_OSR = 256); I <sub>MAG</sub> = 1.28mA; In-phase ADC only; BIOZ_DHPF = 0.002 x SR_BIOZ, BIOZ_DLPF = 0.25 x SR_BIOZ |     | 2280 |      | Αц    |

| BIA Supply Current<br>(GSR/EDA Example)                      | I <sub>AVDD</sub> +<br>I <sub>DVDD</sub> | PLL_CLK = 14.024704MHz, F_BIOZ = 53.5Hz (KDIV = 1024, M = 428, FCLK = 32768Hz, BIOZ_DAC_OSR = 256); BIOZ_DRV_MODE = current; BIOZ_INA_MODE = low power; BIOZ_GAIN = 1V/V; SR_BIOZ = 53.5sps (NDIV = 512, BIOZ_ADC_OSR = 512); I <sub>MAG</sub> = 320nA; In-phase ADC only; Digital filters bypassed                                     |     | 353  | 680  | μΑ    |

| Shutdown Current                                             | I <sub>AVDD</sub> +<br>I <sub>DVDD</sub> | $T_A = +25^{\circ}C$                                                                                                                                                                                                                                                                                                                    |     | 1.0  | 3    | μΑ    |

| Digital I/O Characteristic                                   |                                          | -40°C < T <sub>A</sub> < +85°C                                                                                                                                                                                                                                                                                                          |     |      | 25   |       |

| Input Voltage Low                                            | V <sub>IL</sub>                          | SDI/SDA, SCLK/SCL, TRIG, CSB/<br>I2C_SEL, FCLK                                                                                                                                                                                                                                                                                          |     |      | 0.4  | V     |

| Input Voltage High                                           | V <sub>IH</sub>                          | SDI/SDA, SCLK/SCL, TRIG, CSB/<br>I2C_SEL, FCLK                                                                                                                                                                                                                                                                                          | 1.4 |      |      | V     |

| Input Hysteresis                                             | V <sub>HYS</sub>                         | SDI/SDA, SCLK/SCL, TRIG, CSB/<br>I2C_SEL, FCLK                                                                                                                                                                                                                                                                                          |     | 430  |      | mV    |

| Input Capacitance                                            | $C_{IN}$                                 | SDI/SDA, SCLK/SCL, TRIG, CSB/<br>I2C_SEL, FCLK                                                                                                                                                                                                                                                                                          |     | 10   |      | pF    |

(AVDD = 1.8V, DVDD = 1.8V, FCLK = 32.768Hz,  $T_A$  = +25°C, min/max are from  $T_A$  = -40°C to +85°C, unless otherwise noted, <u>Note 1</u>)

| PARAMETER                                             | SYMBOL               | SYMBOL CONDITIONS MIN TYP MA                       |                                                      |                              |      |      |     |  |  |

|-------------------------------------------------------|----------------------|----------------------------------------------------|------------------------------------------------------|------------------------------|------|------|-----|--|--|

| Input Leakage Current                                 | I <sub>IN</sub>      | SDI/SDA, SCLK/<br>SCL, TRIG, CSB/<br>I2C_SEL, FCLK | T <sub>A</sub> = +25°C, V <sub>IN</sub> = 0V or 1.8V | -0.1                         | 0.01 | +0.1 | μΑ  |  |  |

| Output Voltage Low                                    | $V_{OL}$             | SDO/ADDR, INT                                      | I <sub>SINK</sub> = 4mA                              |                              |      | 0.4  | V   |  |  |

| Output Voltage High                                   | $V_{OH}$             | SDO/ADDR, INT                                      | I <sub>SOURCE</sub> = 4mA                            | V <sub>DVDD</sub> - 0.4      |      |      | V   |  |  |

| Open-Drain Output<br>Voltage Low                      | V <sub>OL_OD</sub>   | INT_OCFG = 0x0                                     | I <sub>SINK</sub> = 4mA                              |                              |      | 0.4  | V   |  |  |

| I <sup>2</sup> C Timing Characteristic                | cs ( <u>Note 3</u> ) |                                                    | •                                                    |                              |      |      |     |  |  |

| 120 Maita Addana                                      |                      | SDO/ADDR = 0                                       |                                                      |                              | D0   |      | Han |  |  |

| I <sup>2</sup> C Write Address                        |                      | SDO/ADDR = 1                                       |                                                      |                              | D2   |      | Hex |  |  |

| 120 D 1 A 1 1                                         |                      | SDO/ADDR = 0                                       |                                                      |                              | D1   |      | l   |  |  |

| I <sup>2</sup> C Read Address                         |                      | SDO/ADDR = 1                                       |                                                      |                              | D3   |      | Hex |  |  |

| Serial Clock Frequency                                | f <sub>SCL</sub>     |                                                    |                                                      | 0                            |      | 400  | kHz |  |  |

| Bus Free Time Between<br>STOP and START<br>Conditions | t <sub>BUF</sub>     |                                                    |                                                      | 1.3                          |      |      | μs  |  |  |

| Hold Time START and<br>Repeat START<br>Condition      | <sup>t</sup> HD,STA  |                                                    |                                                      | 0.6                          |      |      | μs  |  |  |

| SCL Pulse-Width Low                                   | t <sub>LOW</sub>     |                                                    |                                                      | 1.3                          |      |      | μs  |  |  |

| SCL Pulse-Width High                                  | tHIGH                |                                                    |                                                      | 0.6                          |      |      | μs  |  |  |

| Setup Time for a<br>Repeated START<br>Condition       | tsu,sta              |                                                    |                                                      | 0.6                          |      |      | μs  |  |  |

| Data Hold Time                                        | t <sub>HD,DAT</sub>  |                                                    |                                                      | 0                            |      | 900  | ns  |  |  |

| Data Setup Time                                       | t <sub>SU,DAT</sub>  |                                                    |                                                      | 100                          |      |      | ns  |  |  |

| Setup Time for STOP<br>Condition                      | tsu,sto              |                                                    |                                                      | 0.6                          |      |      | μs  |  |  |

| Pulse-Width of<br>Suppressed Spike                    | t <sub>SP</sub>      |                                                    |                                                      | 0                            |      | 50   | ns  |  |  |

| Bus Capacitance                                       | C <sub>B</sub>       |                                                    |                                                      |                              |      | 400  | pF  |  |  |

| SDA and SCL Receiving<br>Rise Time                    | t <sub>R</sub>       | C <sub>B</sub> = bus capacitano                    | ce in pF                                             | 20 + 0.1<br>x C <sub>B</sub> |      | 300  | ns  |  |  |

| SDA and SCL Receiving Fall Time                       | t <sub>F</sub>       | C <sub>B</sub> = bus capacitano                    | ce in pF                                             | 20 + 0.1<br>x C <sub>B</sub> |      | 300  | ns  |  |  |

| SDA Transmitting Fall<br>Time                         | t <sub>TF</sub>      | C <sub>B</sub> = bus capacitance in pF             |                                                      | 20 + 0.1<br>x C <sub>B</sub> |      | 300  | ns  |  |  |

| SPI Timing Characteristi                              | cs ( <u>Note 3</u> ) |                                                    |                                                      |                              |      |      |     |  |  |

| SCLK Frequency                                        | f <sub>SCLK</sub>    |                                                    |                                                      | 0.1                          |      | 24   | MHz |  |  |

| SCLK Period                                           | t <sub>CP</sub>      |                                                    |                                                      | 40                           |      |      | ns  |  |  |

| SCLK Pulse-Width High                                 | t <sub>CH</sub>      |                                                    |                                                      | 18                           |      |      | ns  |  |  |

| SCLK Pulse-Width Low                                  | t <sub>CL</sub>      |                                                    |                                                      | 18                           |      |      | ns  |  |  |

$(\text{AVDD} = 1.8\text{V}, \text{DVDD} = 1.8\text{V}, \text{FCLK} = 32.768\text{Hz}, \text{T}_{A} = +25^{\circ}\text{C}, \text{min/max are from T}_{A} = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{unless otherwise noted}, \\ \underline{\textit{Note 1}})$

| DADAMETED                           | 0)/44001          | 001                                       | IDITIONS                                | 84181                    | T)/D | BAAV | LINUTO |

|-------------------------------------|-------------------|-------------------------------------------|-----------------------------------------|--------------------------|------|------|--------|

| PARAMETER                           | SYMBOL            | CON                                       | IDITIONS                                | MIN                      | TYP  | MAX  | UNITS  |

| CSB Fall to SCLK Rise<br>Setup Time | t <sub>CSS0</sub> | Applies to first SCI CSB goes low.        | _K rising edge after                    | 20                       |      |      | ns     |

| CSB Fall to SCLK Rise<br>Hold Time  | t <sub>CSH0</sub> | Applies to inactive first rising edge.    | rising edge preceding                   | 5                        |      |      | ns     |

| Last SCLK Rise to CSB<br>Rise       | t <sub>CSH1</sub> | Applies to last SCI transaction.          | K rising edge in a                      | 20                       |      |      | ns     |

| Last SCLK Rise to Next<br>CSB Fall  | t <sub>CSF</sub>  | Applies to last SCI<br>CSB falling edge ( | K rising edge to next new transaction). | 60                       |      |      | ns     |

| CSB Pulse-Width High                | t <sub>CSPW</sub> |                                           |                                         | 40                       |      |      | ns     |

| SDI to SCLK Rise Setup<br>Time      | t <sub>DS</sub>   |                                           |                                         | 5                        |      |      | ns     |

| SDI to SCLK Rise Hold<br>Time       | t <sub>DH</sub>   |                                           |                                         | 5                        |      |      | ns     |

| SCLK Fall to SDO<br>Transition      | t <sub>DOT</sub>  | C <sub>LOAD</sub> = 30pF                  |                                         |                          |      | 15   | ns     |

| CSB Fall to SDO<br>Enabled          | t <sub>DOE</sub>  | C <sub>LOAD</sub> = 0pF                   |                                         | 10                       |      |      | ns     |

| CSB Rise to SDO Hi-Z                | t <sub>DOZ</sub>  | Disable Time                              |                                         |                          |      | 5    | ns     |

| TRIG Pulse-Width                    | t <sub>TRIG</sub> |                                           |                                         | 1 x<br>t <sub>FCLK</sub> |      |      | s      |

| ESD PROTECTION                      | •                 |                                           |                                         |                          |      | •    |        |

| E1, E2A, E2B, C1, C2,               |                   | IEC61000-4-2                              | Contact Discharge                       |                          | ±8   |      | kV     |

| C3, C4, E3A, E3B, E4                |                   | 10001000-4-2                              | Air Discharge                           |                          | ±6   |      | ] KV   |

- Note 1: Limits are 100% tested at TA = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. All register settings use default values, unless otherwise noted in specific EC conditions.

- Note 2: Overall accuracy must include calibration resistor accuracy and overall calibration accuracy. Calibration uses an external 32.768kHz, 2.5nsRMS jitter, ±5ppm TC oscillator with a 680Ω external calibration resistor. The calibration resistor and Cole impedance are measured to within 0.05% magnitude and 0.1° phase accuracy using a calibrated Zurich Instruments MFIA.

- **Note 3:** Guaranteed by design and characterization. Not tested in production.

- Note 4: a. BIOZ\_DRV\_MODE = 0x0, IDRV = 160nARMS, F\_BIOZ = 16Hz, SR\_BIOZ = 16sps, BIOZ\_GAIN = 10V/V, BIOZ\_DLPF = 0x4, BIOZ\_AHPF = 24MΩ with external 47nF BIP and BIN capacitors. Effective signal band = DC to 4Hz.

b. BIOZ\_DRV\_MODE = 0x0, IDRV = 32μARMS, F\_BIOZ = 32kHz, SR\_BIOZ = 31.25sps, BIOZ\_GAIN = 10V/V, BIOZ\_DLPF = 0x3, BIOZ\_AHPF = 2kHz. Effective signal band = DC to 2.5Hz.

c. BIOZ\_DRV\_MODE = 0x0, IDRV = 1.28mARMS, F\_BIOZ = 64kHz, SR\_BIOZ = 250sps, BIOZ\_GAIN = 10V/V, BIOZ\_AHPF = 5kHz. Effective signal band = DC to 62.5Hz.

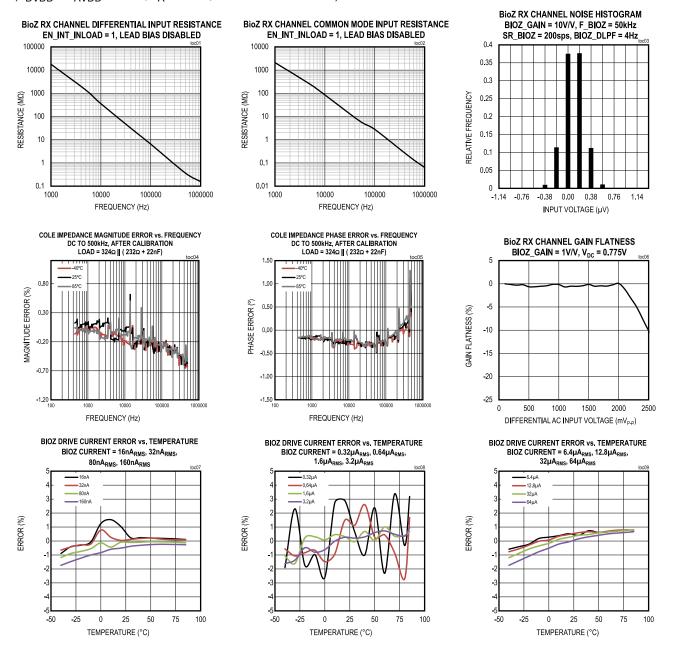

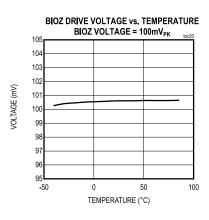

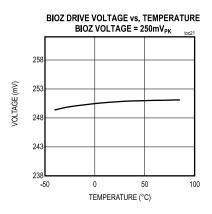

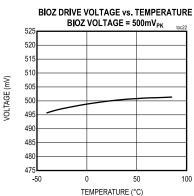

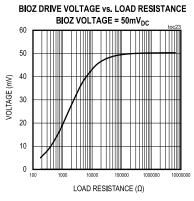

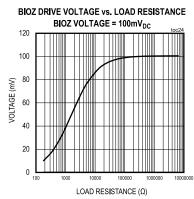

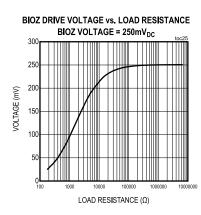

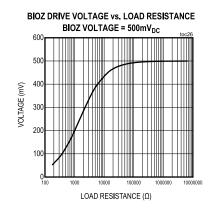

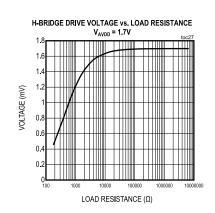

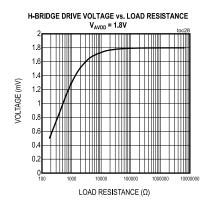

## **Typical Operating Characteristics**

$(V_{DVDD} = V_{AVDD} = +1.8V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

LOAD VOLTAGE (V)

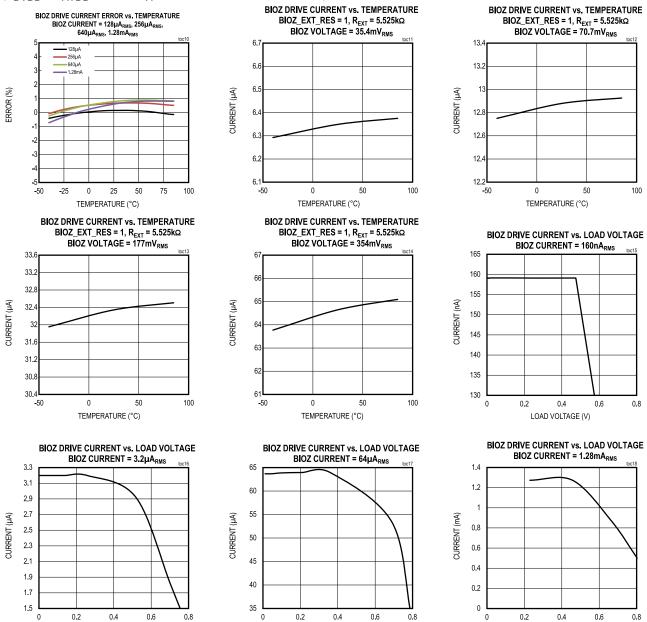

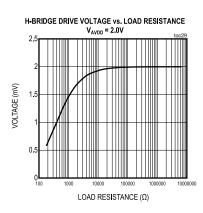

### **Typical Operating Characteristics (continued)**

$(V_{DVDD} = V_{AVDD} = +1.8V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

LOAD VOLTAGE (V)

www.analog.com Analog Devices | 17

LOAD VOLTAGE (V)

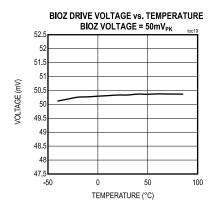

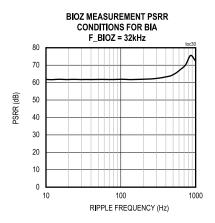

## **Typical Operating Characteristics (continued)**

$(V_{DVDD} = V_{AVDD} = +1.8V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## **Typical Operating Characteristics (continued)**

$(V_{DVDD} = V_{AVDD} = +1.8V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

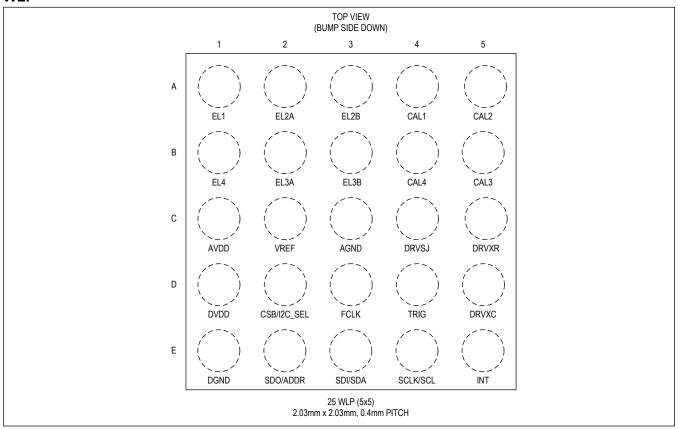

# **Pin Configuration**

## WLP

## **Pin Description**

| PIN           | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power         | •        |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| C1            | AVDD     | Analog Core Supply Voltage. Bypass to AGND with a 0.1µF and a 10µF X5R 0603 capacitor or equivalent effective capacitance.                                                                                                                                                                                                                                                                                                             |

| D1            | DVDD     | Digital Core Supply Voltage. Bypass to DGND with a 0.1μF and a 10μF X5R 0603 capacitor or equivalent effective capacitance.                                                                                                                                                                                                                                                                                                            |

| C3            | AGND     | Analog Power and Reference Ground. Connect to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                    |

| E1            | DGND     | Digital Ground for both Digital Core and I/O Pad Drivers. Recommended to connect to AGND plane.                                                                                                                                                                                                                                                                                                                                        |

| Electrode Con | nections |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A1            | EL1      | Electrode 1 Connection. EL1 is normally connected to the DRVP current generator output, but can be switched to the receive channel's BIP input under program control.                                                                                                                                                                                                                                                                  |

| A2            | EL2A     | Electrode 2A Connection. EL2A or EL2B are normally connected to the receive channel's BIP input, but can be switched to connect to the DRVP current generator output under program control. Two EL2 inputs are provided to use the device for both GSR/EDA applications that require an external AC-coupling capacitor and BIA/BIS applications that use the internal AHPF, and thus do not require an external AC-coupling capacitor. |

| A3            | EL2B     | Electrode 2B Connection. See description for EL2A.                                                                                                                                                                                                                                                                                                                                                                                     |

# Low-Power, High-Performance Bioimpedance Analog Front-End

# **Pin Description (continued)**

| PIN             | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B1              | EL4              | Electrode 4 Connection. EL4 is normally connected to the DRVN current generator output, but can be switched to the receive channel's BIN input under program control.                                                                                                                                                                                                                                                                  |

| B2              | EL3A             | Electrode 3A Connection. EL3A or EL3B are normally connected to the receive channel's BIN input, but can be switched to connect to the DRVN current generator output under program control. Two EL3 inputs are provided to use the device for both GSR/EDA applications that require an external AC-coupling capacitor and BIA/BIS applications that use the internal AHPF, and thus do not require an external AC-coupling capacitor. |

| В3              | EL3B             | Electrode 3B Connection. See description for EL3A.                                                                                                                                                                                                                                                                                                                                                                                     |

| Calibration Su  | ıpport           |                                                                                                                                                                                                                                                                                                                                                                                                                                        |